| 1  | Jon A. Birmingham (Cal. Bar No. 271034)                       |                                   |

|----|---------------------------------------------------------------|-----------------------------------|

| 2  | jbirmi@fitcheven.com FITCH, EVEN, TABIN & FLANNERY LLP        |                                   |

| 3  | 21700 Oxnard Street, Suite 1740                               |                                   |

| 4  | Woodland Hills, California 91367<br>Telephone: (818) 715-7025 |                                   |

|    | Facsimile: (818) 715-7033                                     |                                   |

| 5  | Attorney for Plaintiff,                                       |                                   |

| 6  | LONE STAR SILICON INNOVATIONS LLC                             |                                   |

| 7  |                                                               |                                   |

| 8  |                                                               | DISTRICT COURT ICT OF CALIFORNIA  |

| 9  |                                                               | ISCO DIVISION                     |

| 10 |                                                               |                                   |

| 11 | LONE STAR SILICON INNOVATIONS LLC,                            | Case No. 3:17-cv-07206            |

| 12 | Plaintiff,                                                    | COMPLAINT FOR PATENT INFRINGEMENT |

| 13 | v.                                                            |                                   |

| 14 | STMICROELECTRONICS, INC., AND                                 | DEMAND FOR JURY TRIAL             |

| 15 | STMICROELECTRONICS N.V.                                       |                                   |

| 16 | Defendants.                                                   |                                   |

| 17 |                                                               |                                   |

| 18 |                                                               | J                                 |

| 19 |                                                               |                                   |

| 20 |                                                               |                                   |

| 21 |                                                               |                                   |

| 22 |                                                               |                                   |

|    |                                                               |                                   |

| 23 |                                                               |                                   |

| 24 |                                                               |                                   |

| 25 |                                                               |                                   |

| 26 |                                                               |                                   |

| 27 |                                                               |                                   |

| 28 |                                                               |                                   |

|    | Complaint for Patent Infringement Case No. 3:17-cv-07206      |                                   |

"Defendants") as follows:

## 4

5 6 7

#### 8

9

10

11 12

13

15

16 17

18

19

20 21

22

23

24

25

26

27

28

STMicroelectronics N.V. and STMicroelectronics, Inc. (individually or collectively "STMicro" or

#### NATURE OF ACTION

Plaintiff, Lone Star Silicon Innovations LLC ("Lone Star"), complains against Defendants

1. This is an action for patent infringement of United States Patent Nos. 5,912,188; 6,153,933; and 6,388,330 (collectively, the "Patents in Suit") under the Patent Laws of the United States, 35 U.S.C. § 1, et seq. through STMicro's importation, offer for sale, and sale of semiconductor devices.

#### THE PARTIES

- 2. Plaintiff Lone Star is a corporation organized and existing under the laws of the State of Texas with its principal place of business at 8105 Rasor Blvd., Suite 210, Plano, TX 75024. Lone Star is in the business of licensing patented technology. Lone Star is the assignee of the Patents in Suit.

- 3. Upon information and belief, Defendant STMicroelectronics N.V. (hereinafter "STMicro N.V.") is a corporation organized under the laws of The Netherlands, with its principal place of business at WTC Schiphol Airport, Schiphol Boulevard 265, 1118 BH Schiphol, The Netherlands. Defendant STMicro N.V. has a headquarters and operational offices located at 39 Chemin du Champ des Filles, 1228 Plan-Les-Ouates, Geneva, Switzerland. Defendant STMicro N.V. conducts business and is doing business in California and in this District and elsewhere in the United States, including, without limitation, using, promoting, offering to sell, importing, and/or selling integrated circuit devices that embody and/or are made using the patented technology, and enabling end-user purchasers to use such devices in this District. STMicro N.V.'s agent for service of process in the United States is Corporation Service Company (CSC), 80 State Street, Albany, New York, 12207.

- 4. Defendant STMicroelectronics, Inc. (hereinafter "STMicro Delaware") is a corporation incorporated under the laws of Delaware with its Americas Region headquarters at 750 Canyon Drive, Suite 300, Coppell, TX 75019. STMicro Delaware also has places of business at 2755 Great America Way, 3<sup>rd</sup> Floor, Santa Clara, CA 95054 and 25215 Augustine Drive, Santa Clara, CA 95054. STMicro Delaware's agent for service of process in California is CT Corporation System, 818 W. 7th Street, Suite 930, Los Angeles, CA 90017. Defendant STMicro Delaware conducts business in California and in this District and elsewhere in the United States, including, without limitation, using, promoting, offering to

sell, importing and/or selling semiconductor devices and/or devices that incorporate such devices that

embody the patented technology, and enabling end-user purchasers to use such devices in this District.

3

# 4

5

6 7

8 9

10 11

12 13

15 16

17

18

19

20 21

22

23

24

25

26 27

28

JURISDICTION AND VENUE

- 5. This action arises under the Patent Laws of the United States, Title 35 of the United States Code. This Court has subject matter jurisdiction over this action pursuant to 28 U.S.C. §§ 1331 and 1338(a).

- 6. On information and belief, Defendants are subject to this Court's specific and general personal jurisdiction pursuant to due process and/or the California Long Arm Statute, due at least to their substantial business conducted in this forum, directly and/or through intermediaries, including (i) having solicited business in the State of California, transacted business within the State of California and attempted to derive financial benefit from residents of the State of California, including benefits directly related to the instant patent infringement causes of action set forth herein; (ii) having placed their products and services into the stream of commerce throughout the United States and having been actively engaged in transacting business in California and in this District; and (iii) either alone or in conjunction with others, having committed acts of infringement within California and in this District. On information and belief, Defendants, directly and/or through intermediaries, have advertised (including through websites), offered to sell, sold and/or distributed infringing products, and/or have induced the sale and use of infringing products in the United States and in California. Defendants have, directly or through their distribution network, purposefully and voluntarily placed such products in the stream of commerce knowing and expecting them to be purchased and used by consumers in California and in this District. Defendants have either committed direct infringement in California or committed indirect infringement based on acts of direct infringement in California and from their locations in Santa Clara, CA. Further, on information and belief, Defendants are subject to the Court's general jurisdiction, including from regularly doing or soliciting business, engaging in other persistent courses of conduct, and/or deriving substantial revenue from products and services provided to individuals in California and in this District.

- 7. On information and belief, Defendants do one or more of the following with semiconductor devices and/or devices that incorporate such devices that that they manufacture: (a) import these devices into the United States for sale to customers, including customers in California; (b) sell them

4 5

6 7

8 9

10

11

12 13

15

16

17

18

judicial district.

19

20

21

22

23

24

25

26

27

28

or offer them for sale in the United States, including to customers in California; and (c) sell them to customers who incorporate them into products that such customers import, sell, or offer for sale in the United States, including in California.

8. Venue is proper in this Court pursuant to 28 U.S.C. §§ 1391 and 1400 because Defendants have a regular and established place of business within this District and have committed acts of infringement within the District. Defendants maintain and operate at least two facilities within this District in Santa Clara. Defendants' acts of infringement within this District include, but are not limited to, selling and offering to sell infringing products within the District. Defendants' Santa Clara facilities have over 200 employees and host regional sales and technical marketing services for networking equipment, TV and monitor products, printers, CMOS devices, bipolar/CMOS/DMOS mixed signal devices. hard-disk other (See technology, gaming and consumer products. www.stmicroelectronics.com.cn/content/st com/en/about/careers/stlocations/americas/united\_states/santa\_clara.html). Without limitation, on information and belief, within this District, Defendants, directly and/or through intermediaries, have advertised (including through websites), offered to sell, sold and/or distributed infringing products, and/or have induced the sale and use of infringing products. In addition, venue is proper in this District for Defendant STMicro N.V. pursuant to 28 U.S.C. § 1391(c)(3) because it is not resident in the United States, and therefore may be sued in any

### **INTRADISTRICT ASSIGNMENT**

9. Pursuant to Civil L.R. 3-5(b) Lone Star notes that there are six cases involving at least one patent in common pending in the San Francisco Division before the Honorable William H. Alsup.

#### THE PATENTS IN SUIT

10. On June 15, 1999, U.S. Patent No. 5,912,188 ("the '188 patent"), entitled "Method Of Forming A Contact Hole In An Interlevel Dielectric Layer Using Dual Etch Stops," a copy of which is attached hereto as Exhibit A, was duly and legally issued. The '188 patent issued from U.S. patent application Serial Number 08/905,686 filed August 4, 1997, and discloses and relates to the design of and processes for fabricating semiconductor memory devices. The inventors assigned all right, title, and interest in the '188 patent to Advanced Micro Devices, Inc. (hereinafter "AMD"). AMD assigned its entire

7

11 12

10

13

16

15

18

17

19 20

21

22

23

25

26

27 28 right, title, and interest in the '188 patent to Lone Star, and Lone Star is the sole owner of all rights, title, and interest in and to the '188 patent including the right to sue for and collect past, present, and future damages and to seek and obtain injunctive or any other relief for infringement of the '188 patent.

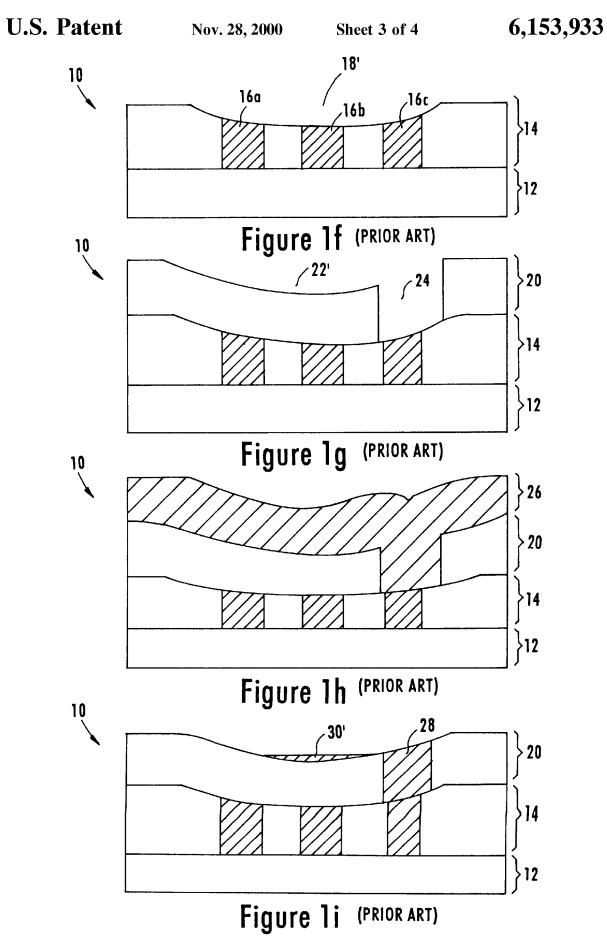

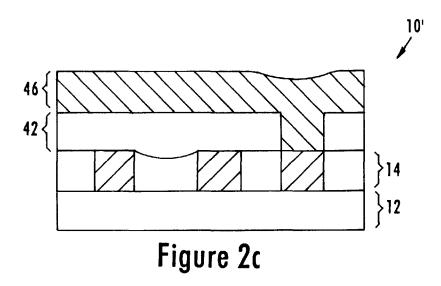

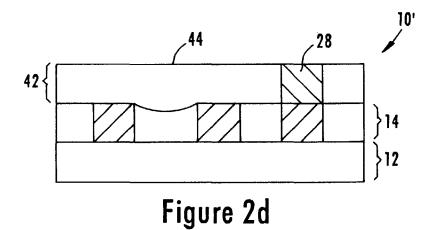

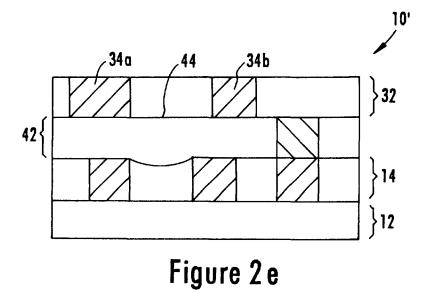

- 11. On November 28, 2000, U.S. Patent No. 6,153,933 ("the '933 patent"), entitled "Elimination of Residual Materials in a Multiple-Layer Interconnect Structure," a copy of which is attached hereto as Exhibit B, was duly and legally issued. The '933 patent issued from U.S. patent application Serial Number 08/925,821 filed September 5, 1997, and discloses and relates to the design of and processes for fabricating semiconductor devices. The inventors assigned all right, title, and interest in the '933 patent to AMD assigned its entire right, title, and interest in the '933 patent to Lone Star, and Lone Star is the sole owner of all rights, title, and interest in and to the '933 patent including the right to sue for and collect past, present, and future damages and to seek and obtain injunctive or any other relief for infringement of the '933 patent.

- 12. On May 14, 2002, U.S. Patent No. 6,388,330 ("the '330 patent"), entitled "Low Dielectric Constant Etch Stop Layers In Integrated Circuit Interconnects," a copy of which is attached hereto as Exhibit C, was duly and legally issued. The '330 patent issued from U.S. patent application Serial Number 09/776,012 filed February 1, 2001, and discloses and relates to the design of and processes for fabricating semiconductor devices. The inventors assigned all right, title, and interest in the '330 patent to AMD. AMD assigned its entire right, title, and interest in the '330 patent to Lone Star, and Lone Star is the sole owner of all rights, title, and interest in and to the '330 patent including the right to sue for and collect past, present, and future damages and to seek and obtain injunctive or any other relief for infringement of the '330 patent.

#### DEFENDANTS' INFRINGING PRODUCTS AND METHODS

13. Defendants are in the business of manufacturing semiconductor devices. Using their own processes and techniques, Defendants make, use, sell, offer for sale, and/or import into the United States semiconductor devices, including discrete and standard commodity components, application specific integrated circuits ("ASICs"), full custom devices and semi-custom devices and application-specific standard products ("ASSPs"), CMOS, Bi-CMOS, bipolar and non-volatile memory, fully depleted silicon on insulator ("FD-SOI"), radio frequency silicon-on-insulator ("RF-SOI"), diffused metal-on-silicon

oxide semiconductor ("DMOS"), and silicon carbide ("SiC") integrated circuit devices and products incorporating such devices. Defendants' products are used in a variety of industrial, automotive, and consumer electronics, including mobile phones, IoT devices, power conversion products, metering devices for smart grids, tablets, computers, cameras, set-top boxes, global positioning receivers, data loggers, sports accessories, and networking devices. Defendants also provide a FD-SOI Technology Platform to support standard cells, memories, IO (input/output) libraries, clock generators, and specific IPs, which are used as building blocks in different chip designs. Defendants' sales in the U.S. and North America are made through Defendant STMicro Delaware.

14. Despite not having a license to the '188 and '933 patents, Defendants have used the semiconductor fabrication methods claimed therein in making semiconductor devices and have used, sold, offered for sale, and imported in the United States semiconductor devices manufactured using such claimed methods. Despite not having a license to the '330 patents, Defendants' semiconductor devices adopt the designs claimed by those patents.

#### FIRST CAUSE OF ACTION – INFRINGEMENT OF THE '188 PATENT

- 15. Plaintiff hereby repeats and re-alleges the allegations contained in paragraphs 1 to 14, as if fully set forth herein.

- Defendants directly and/or through their subsidiaries, affiliates, agents, and/or business partners, have in the past and continue to directly infringe the '188 patent pursuant to 35 U.S.C. § 271(g) by importing, using, selling, or offering to sell semiconductor devices in the United States made using the methods claimed in the '188 patent, including at least claims 3, 11-13, and 19. On information and belief, semiconductor devices manufactured by Defendants and/or other related entities and/or business partner foundries, are made using a process that practices claims 3, 11-13, and 19 including the steps of: (a) providing a semiconductor substrate; (b) forming a gate over the substrate; (c) forming a source/drain region in the substrate; (d) providing a source/drain contact electrically coupled to the source/drain region; (e) forming an interlevel dielectric layer that includes first, second and third dielectric layers over the source/drain contact; (f) forming an etch mask over the interlevel dielectric layer; (g) applying a first etch which is highly selective of the first dielectric layer with respect to the second dielectric layer through an opening in the etch mask using the second dielectric layer as an etch stop, to form a first hole in the first

9

10

11

12

13

15

16

17

18

19

20

21

22

23

25

26

27

28

dielectric layer that extends to the second dielectric layer without extending to the third dielectric layer; (h) applying a second etch which is highly selective of the second dielectric layer with respect to the third dielectric layer through the opening in the etch mask using the third dielectric layer as an etch stop, to form a second hole in the second dielectric layer that extends to the third dielectric layer without extending to the source/drain contact; and (i) applying a third etch which is highly selective of the third dielectric layer with respect to the source/drain contact through the opening in the etch mask, to form a third hole in the third dielectric layer that extends to the source/drain contact, such that the first, second and third holes in combination provide a contact hole in the interlevel dielectric layer.

- 17. Defendants directly and/or through their subsidiaries, affiliates, agents, and/or business partners, have also in the past and continue to directly infringe the '188 patent, including at least claims 3, 11-13, and 19, pursuant to 35 U.S.C. § 271(g) by importing, using, selling, or offering to sell semiconductor devices in the United States made using the methods claimed in the '188 patent. The semiconductor devices manufactured by Defendants and/or other entities owned and controlled by Defendants or by third-party partner foundries under contract with Defendants, are made using a process that practices the claims of the '188 patent. Defendants directly infringe when they import, use, sell, or offer for sale in the United States semiconductor devices made using the claimed methods.

- 18. Defendants have been and are engaged in one or more of these direct infringing activities related to their semiconductor devices, including at least their 5869BA – 4Mp, 2.0µm Pixel Pitch Back Illuminated CMOS Image Sensor, and any other semiconductor devices made using a substantially similar process and including transistors having a contact hole extending through first, second, and third dielectric layers to a source/drain contact formed using a process involving dual etch stops in according with the methods of claims 3, 11-13, and 19 of the '188 patent ("'188 Accused Products").

- 19. Defendants, directly and/or through their subsidiaries, affiliates, agents, and/or business partners, have been and are now indirectly infringing the '188 patent, including at least claims 3, 11-13, and 19, pursuant to 35 U.S.C. § 271(b) by actively inducing acts of direct infringement performed by others. Defendants have actual notice of the '188 patent and the infringement alleged herein on or about November 14, 2016, which was the date that Lone Star's counsel sent a letter to Defendants, attention Raj Krishnan, providing notice of Defendants' infringement of the '188 patent. In addition, upon information

10

11

12

13

15

16

17

18

19

20

21

22

23

24

25

26

27

28

- technology in the fields of the Patents in Suit, specifically including patents directed to semiconductor devices issued to competitors such as AMD, the original assignee of the '188 patent. Upon information and belief, Defendants are assignees of 1,862 patents, including at least 15 patents prosecuted in the USPTO in the same classifications as the '188 patent, providing Defendants intimate knowledge of the art in fields relevant to this civil action. The timing, circumstances and extent of Defendants obtaining actual knowledge of the '188 patent prior to the commencement of this lawsuit will be confirmed during discovery.

- 20. Upon gaining knowledge of the '188 patent, it was, or became, apparent to Defendants that the manufacture, sale, importation, offer for sale, and use of their '188 Accused Products result in infringement of the '188 patent. Upon information and belief, Defendants have continued and will continue to engage in activities constituting inducement of infringement, notwithstanding their knowledge, or willful blindness thereto, that the activities they induce result in infringement of the '188 patent.

- 21. The '188 Accused Products are intended for integration into products known to be sold widely in the United States. Defendants make semiconductor devices using methods claimed in the '188 patent, which devices infringe when they are imported into, or sold, used, or offered for sale in, the United States. Defendants indirectly infringe by inducing customers (such as makers of mobile devices, cameras, and other devices) to import products that integrate semiconductor devices made using the methods claimed in the '188 patent, or to sell or use such products, or offer them for sale, in the United States.

- 22. Defendants encourage customers, resellers, OEMs, or others to import into the United States and sell and use in the United States the '188 Accused Products made using the methods claimed in the '188 patent with knowledge and the specific intent to cause the acts of direct infringement performed by these third parties. On information and belief, after Defendants obtained knowledge of the '188 patent, the '188 Accused Products have been and will continue to be imported into the United States and sold in large volumes by themselves and by others, such as customers, distributors, and resellers. Defendants are aware that the '188 Accused Products are always made using the same fabrication methods under

2 | '1 | 3 | im 4 | pa

5

6

7 8 9

11 12

10

13

1516

17

18 19

20

2122

23

2425

26

2728

Defendants' direction and control such that Defendants' customers will infringe one or more claims of the '188 patent by incorporating such semiconductor devices in other products, and that subsequent importation, sale, and use of such products in the United States would be a direct infringement of the '188 patent. Therefore, Defendants are aware that their customers will infringe the '188 patent by importing, selling, and using the products supplied by Defendants.

- 23. Defendants directly benefit from and actively and knowingly encourage customers', resellers', and users' importation of these products into the United States and sale and use within the United States. Defendants actively encourage customers and downstream users, OEMs, and resellers to import, use, and sell in the United States the '188 Accused Products that they manufacture and supply, including through advertising, marketing, and sales activities directed at United States sales. On information and belief, Defendants are aware of the size and importance of the United States market for customers of Defendants' products, and also distribute or supply these products intended for importation, use, and sale in the United States. Defendants routinely market their infringing semiconductor products to third parties for inclusion in products that are sold to customers in the United States, as well as directly to end-user customers. For example, Defendants have publicly stated that their semiconductor devices are primarily targeted for use in industrial, automotive, and consumer electronics, including mobile phones, tablets, computers, cameras, set-top boxes, global positioning receivers, data loggers, sports accessories, networking devices, IoT devices, power conversion devices, and metering devices for smart grids. Further, Defendants have publicly stated that their CMOS image sensor products are primarily targeted for imaging applications in the automotive, security, gaming, medical, and high-end traditional camera markets, of whose products are widely sold and used in the United States. Defendants have numerous direct sales, distributors, and reseller outlets for these products in the United States. Defendants' marketing efforts show that they have specifically intended to and have induced direct infringement in the United States.

- 24. Defendants also provide OEMs, manufacturers, importers, resellers, customers, and end users instructions, user guides, and technical specifications on how to incorporate the '188 Accused Products into electronics products that are made, used, sold, offered for sale in, and/or imported into the United States. When OEMs, manufacturers, importers, resellers, customers, and end users follow such instructions, user guides, and technical specifications and embed the products in end products and make,

use, offer to sell, sell, or import them into the United States, they directly infringe one or more claims of the '188 patent. Defendants know that by providing such instructions, user guides, and technical specifications, OEMs, manufacturers, importers, resellers, customers, and end users follow them, and therefore directly infringe one or more claims of the '188 patent. Defendants thus know that their actions actively induce infringement.

- 25. Defendants have engaged and continue to engage in additional activities to specifically target the United States market for the '188 Accused Products and actively induce OEMs, manufacturers, importers, resellers, customers, and end users to directly infringe one or more claims of the '188 patent in the United States. For example, Defendants have showcased their CMOS image sensor technologies at various industry events and through written materials distributed in the United States, in an effort to encourage various OEMs, manufacturers, importers, resellers, customers, and end users to include the infringing technology in their computers, mobile devices, cameras and other products. These events are attended by the direct infringers mentioned above and generally by companies that make, use, offer to sell, sell, or import in the United States products that use semiconductor devices such as those made by Defendants.

- 26. Defendants derive significant revenue by selling their semiconductor products to third parties who directly infringe the '188 patent in the United States.

- 27. Defendants' extensive sales and marketing efforts, sales volume, and partnerships all evidence their intent to induce companies to infringe one or more claims of the'188 patent by, using, offering to sell, selling, or importing products that incorporate the '188 Accused Products in the United States. Defendants have had specific intent to induce infringement or have been willfully blind to the direct infringement they are inducing.

- 28. Defendants' direct and indirect infringement of the '188 patent has injured Lone Star, and Lone Star is entitled to recover damages adequate to compensate for such infringement pursuant to 35 U.S.C. § 284. Unless they cease their infringing activities, Defendants will continue to injure Lone Star by infringing the '188 patent.

- 29. On information and belief, Defendants acted egregiously and with willful misconduct in that their actions constituted direct or indirect infringement of a valid patent, and this was either known

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

or so obvious that Defendants should have known about it. Defendants continue to infringe the '188 patent by using, selling, offering for sale, and importing in the United States the '188 Accused Products and to induce the direct infringement of others performing these acts, or they have acted at least in reckless disregard of Lone Star's patent rights. On information and belief, Defendants will continue their infringement notwithstanding actual knowledge of the '188 patent and without a good faith basis to believe that their activities do not infringe any valid claim of the '188 patent. All infringement of the '188 patent following Defendants' knowledge of the '188 patent is willful and Lone Star is entitled to treble damages and attorneys' fees and costs incurred in this action under 35 U.S.C. §§ 284 and 285.

#### SECOND CAUSE OF ACTION – INFRINGEMENT OF THE '933 PATENT

- 30. Plaintiff hereby repeats and re-alleges the allegations contained in paragraphs 1 to 14, as if fully set forth herein.

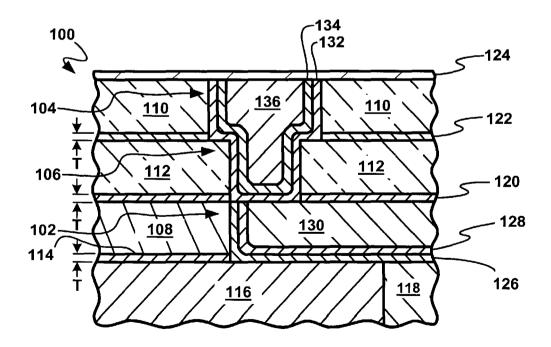

- 31. Defendants, directly and/or through their subsidiaries, affiliates, agents, and/or business partners, have in the past and continue to directly infringe the '933 patent pursuant to 35 U.S.C. § 271(g) by importing, using, selling, or offering to sell semiconductor devices in the United States made using the methods claimed in the '933 patent, including at least claims 5-12. On information and belief, semiconductor devices manufactured by Defendants and/or other related entities and/or business partner foundries, are made using a process that practices claims 5-12 including the steps of: (a) forming a first layer interconnect having a first dielectric layer though which a first layer conductor extends; (b) forming a second layer interconnect on the first layer interconnect, the second layer interconnect having a second layer dielectric through which at least one second layer conductor extends, by forming the second layer dielectric to a first thickness and substantially planarizing the second layer dielectric to reduce the first thickness to a second thickness prior to patterning the second layer dielectric; (c) patterning the second layer dielectric to form an etched opening; and (d) filling the etched opening with a conductive material to form the second layer conductor.

- 32. Defendants directly and/or through their subsidiaries, affiliates, agents, and/or business partners, have also in the past and continue to directly infringe the '933 patent, including at least claims 5-12, pursuant to 35 U.S.C. § 271(g) by importing, using, selling, or offering to sell semiconductor devices in the United States made using the methods claimed in the '933 patent. The semiconductor devices

13 14

1516

17

18

1920

21

22

2324

25

2627

28

Complaint for Patent Infringement

Case No. 3:17-cv-07206

manufactured by Defendants and/or other entities owned and controlled by Defendants or by third-party partner foundries under contract with Defendants, are made using a process that practices the claims of the '933 patent. Defendants directly infringe when they import, use, sell, or offer for sale in the United States semiconductor devices made using the claimed methods.

- 33. Defendants have been and are engaged in one or more of these direct infringing activities related to their semiconductor devices, including at least their CMOSIS X1000 CMOS Image Sensor, and any other semiconductor devices having first and second interconnect layers designed in accordance with claims 5-12 of '933 patent and having a substantially similar design ("the '933 Accused Products").

- 34. Defendants, directly and/or through their subsidiaries, affiliates, agents, and/or business partners, have been and are now indirectly infringing the '933 patent, including at least claims 5-12, pursuant to 35 U.S.C. § 271(b) by actively inducing acts of direct infringement performed by others. Defendants had actual notice of the '933 patent and the infringement alleged herein on or about November 14, 2016, which was the date that Lone Star's counsel sent a letter to Defendants, attention Raj Krishnan, providing notice of Defendants' infringement of the '933 patent. In addition, upon information and belief, Defendants have numerous lawyers and other active agents of Defendants and of their owned and controlled subsidiaries who regularly review patents and published patent applications relevant to technology in the fields of the Patents in Suit, specifically including patents directed to semiconductor devices issued to competitors such as AMD, the original assignee of the '933 patent. Upon information and belief, Defendants are assignees of 1,862 patents, including at least 23 patents prosecuted in the USPTO in the same classifications as the '933 patent, providing Defendants intimate knowledge of the art in fields relevant to this civil action. The timing, circumstances, and extent of Defendants obtaining actual knowledge of the '933 patent prior to the commencement of this lawsuit will be confirmed during discovery.

- 35. Upon gaining knowledge of the '933 patent, it was, or became, apparent to Defendants that the manufacture, sale, importing, offer for sale, and use of their '933 Accused Products result in infringement of the '933 patent. Upon information and belief, Defendants have continued and will continue to engage in activities constituting inducement of infringement, notwithstanding their

5 6

7

8

9

10

11 12

14 15

13

16

17

18 19

20

21

22

23

24

26

27

28

knowledge, or willful blindness thereto, that the activities they induce result in infringement of the '933 patent under 35 U.S.C. § 271(b).

- 36. The '933 Accused Products are intended for integration into products known to be sold widely in the United States. Defendants make semiconductor devices that embody the inventions claimed in the '933 patent, which devices infringe when they are imported into, or sold, used, or offered for sale in, the United States. Defendants indirectly infringe by inducing customers (such as makers of mobile devices, cameras, and other devices) to import products that integrate semiconductor devices embodying inventions claimed in the '933 patent, or to sell or use such products, or offer them for sale, in the United States.

- 37. Defendants encourage customers, resellers, OEMs, or others to import into the United States and sell and use in the United States the '933 Accused Products embodying inventions claimed in the '933 patent with knowledge and the specific intent to cause the acts of direct infringement performed by these third parties. On information and belief, after Defendants obtained knowledge of the '933 patent, the '933 Accused Products have been and will continue to be imported into the United States and sold in large volumes by themselves and by others, such as customers, distributors, and resellers. Defendants are aware that the '933 Accused Products are integral components of the computer, camera, and mobile products incorporating them, that the infringing semiconductor devices are built into the computer and other products, and cannot be removed or disabled by a purchaser of the consumer products containing the infringing devices, such that Defendants' customers will infringe one or more claims of the '933 patent by incorporating such semiconductor devices in other products, and that subsequent importation, sale, and use of such products in the United States would be a direct infringement of the '933 patent. Therefore, Defendants are aware that their customers will infringe one or more claims of the '933 patent by selling, offering for sale, importing, and/or using the products as-sold and as-marketed by Defendants.

- 38. Defendants directly benefit from and actively and knowingly encourage customers', resellers', and users' importation of these products into the United States and sale and use within the United States. Defendants actively encourage customers and downstream users, OEMs, and resellers to import, use, and sell in the United States the '933 Accused Products that they manufacture and supply, including through advertising, marketing, and sales activities directed at United States sales. On

information and belief, Defendants are aware of the size and importance of the United States market for customers of Defendants' products, and also distribute or supply these products intended for importation, use, and sale in the United States. Defendants routinely market their infringing semiconductor devices to third parties for inclusion in products that are sold to customers in the United States, as well as directly to end-user customers. For example, Defendants have publicly stated that their semiconductor devices are primarily targeted for use in industrial, automotive, and consumer electronics, including mobile phones, tablets, computers, cameras, set-top boxes, global positioning receivers, data loggers, sports accessories, networking devices, IoT devices, power conversion devices, and metering devices for smart grids. Further, Defendants have publicly stated that their CMOS image sensor products are primarily targeted for imaging applications in the automotive, security, gaming, medical, and high-end traditional camera markets, of whose products are widely sold and used in the United States. Defendants have numerous direct sales, distributors, and reseller outlets for these products in the United States. Defendants' marketing efforts show that they have specifically intended to and have induced direct infringement in the United States.

- 39. Defendants also provide OEMs, manufacturers, importers, resellers, customers, and end users instructions, user guides, and technical specifications on how to incorporate the '933 Accused Products into electronics products that are made, used, sold, offered for sale in, and/or imported into the United States. When OEMs, manufacturers, importers, resellers, customers, and end users follow such instructions, user guides, and technical specifications and embed the products in end products and make, use, offer to sell, sell, or import them into the United States, they directly infringe one or more claims of the '933 patent. Defendants know that by providing such instructions, user guides, and technical specifications, OEMs, manufacturers, importers, resellers, customers, and end users follow them, and therefore directly infringe one or more claims of the '933 patent. Defendants thus know that their actions actively induce infringement.

- 40. Defendants have engaged and continue to engage in additional activities to specifically target the United States market for the '933 Accused Products and actively induce OEMs, manufacturers, importers, resellers, customers, and end users to directly infringe one or more claims of the '933 patent in the United States. For example, Defendants have showcased their CMOS image sensor technologies at various industry events and through written materials distributed in the United States, in an effort to

encourage various OEMs, manufacturers, importers, resellers, customers, and end users to include the infringing technology in their computers, mobile devices, removable storage devices, and other products. These events are attended by the direct infringers mentioned above and generally by companies that make, use, offer to sell, sell, or import in the United States products that use semiconductor devices such as those made by Defendants.

- 41. Defendants derive significant revenue by selling the '933 Accused Products to third parties who directly infringe the '933 patent in the United States.

- 42. Defendants' extensive sales and marketing efforts, sales volume, and partnerships all evidence their intent to induce companies to infringe one or more claims of the '933 patent by, using, offering to sell, selling, or importing products that incorporate the '933 Accused Products in the United States. Defendants have had specific intent to induce infringement or have been willfully blind to the direct infringement they are inducing.

- 43. Defendants' direct and indirect infringement of the '933 patent has injured Lone Star, and Lone Star is entitled to recover damages adequate to compensate for such infringement pursuant to 35 U.S.C. § 284. Unless they cease their infringing activities, Defendants will continue to injure Lone Star by infringing the '933 patent.

- On information and belief, Defendants acted egregiously and with willful misconduct in that their actions constituted direct or indirect infringement of a valid patent, and this was either known or so obvious that Defendants should have known about it. Defendants continue to infringe the '933 patent by using, selling, offering for sale, and importing in the United States the '933 Accused Products and to induce the direct infringement of others performing these acts, or they have acted at least in reckless disregard of Lone Star's patent rights. On information and belief, Defendants will continue their infringement notwithstanding actual knowledge of the '933 patent and without a good faith basis to believe that their activities do not infringe any valid claim of the '933 patent. All infringement of the '933 patent following Defendants' knowledge of the '933 patent is willful and Lone Star is entitled to treble damages and attorneys' fees and costs incurred in this action under 35 U.S.C. §§ 284 and 285.

#

#

#

#### THIRD CAUSE OF ACTION – INFRINGEMENT OF THE '330 PATENT

- 45. Plaintiff hereby repeats and re-alleges the allegations contained in paragraphs 1 to 14, as if fully set forth herein.

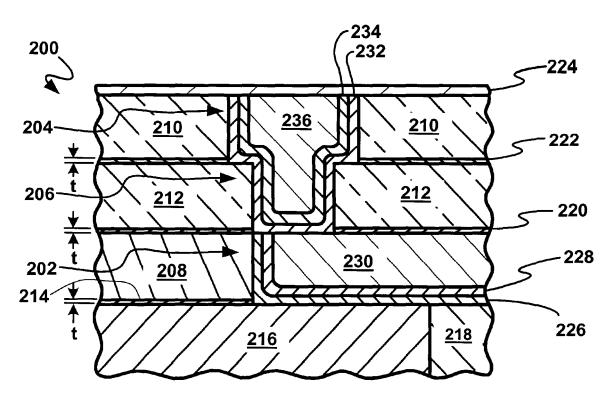

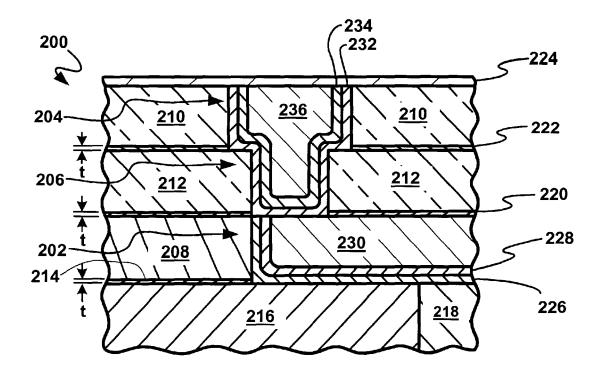

- 46. Defendants, directly and/or through their subsidiaries, affiliates, agents, and/or business partners, have in the past and continue to directly infringe the '330 patent, including at least claims 1, 4, and 5, pursuant to 35 U.S.C. § 271(a) by using, selling, offering to sell, and/or importing semiconductor devices that embody the inventions claimed in the '330 patent, within the United States and within this District. In violation of the '330 patent, for example, Defendants' accused semiconductor devices include: (a) a semiconductor substrate having a semiconductor device provided thereon; (b) a first dielectric layer formed over the semiconductor substrate having a first opening; (c) a first conductor core filling the first opening and connected to the semiconductor device; (d) an etch stop layer of silicon nitride formed over the first dielectric layer and the first conductor core, the etch stop layer having a dielectric constant below 5.5; (e) a second dielectric layer formed over the etch stop layer and having a second opening open to the first conductor core; and (f) a second conductor core filling the second opening and connected to the first conductor core.

- 47. Defendants have been and are engaged in one or more of these direct infringing activities related to their semiconductor devices, including at least their STA8088 Satellite Receiver, and any other semiconductor devices having transistor interconnects designed in accordance with claims 1, 4, and 5 of the '330 patent and having a substantially similar design ("the '330 Accused Products").

- 48. Defendants, directly and/or through their subsidiaries, affiliates, agents, and/or business partners, have been and are now indirectly infringing the '330 patent, including at least claims 1, 4, and 5, pursuant to 35 U.S.C. § 271(b) by actively inducing acts of direct infringement performed by others. Defendants had actual notice of the '330 patent and the infringement alleged herein on or about November 14, 2016, which was the date that Lone Star's counsel sent a letter to Defendants, attention Raj Krishnan, providing notice of Defendants' infringement of the '330 patent. In addition, upon information and belief, Defendants have numerous lawyers and other active agents of Defendants and of their owned and controlled subsidiaries who regularly review patents and published patent applications relevant to technology in the fields of the Patents in Suit, specifically including patents directed to semiconductor

10 11

12

13 15

16 17

19

20

18

21 22

23 24

25

26 27

28

devices issued to competitors such as AMD, the original assignee of the '330 patent. Upon information and belief, Defendants are assignees of 1,862 patents, including at least 19 patents prosecuted in the USPTO in the same classifications as the '330 patent, giving Defendants intimate knowledge of the art in fields relevant to this civil action. The timing, circumstances and extent of Defendants obtaining actual knowledge of the '330 patent prior to the commencement of this lawsuit will be confirmed during discovery.

- 49. Upon gaining knowledge of the '330 patent, it was, or became, apparent to Defendants that the manufacture, sale, importing, offer for sale, and use of its '330 Accused Products result in infringement of the '330 patent. Upon information and belief, Defendants have continued and will continue to engage in activities constituting inducement of infringement, notwithstanding their knowledge, or willful blindness thereto, that the activities they induce result in infringement of the '330 patent under 35 U.S.C. § 271(b).

- 50. The '330 Accused Products are intended for integration into products known to be sold widely in the United States. Defendants make semiconductor devices that embody the inventions claimed in the '330 patent, which devices infringe when they are imported into, or sold, used, or offered for sale in the United States. Defendants indirectly infringe by inducing customers (such as makers of mobile devices, handheld computers, cameras, data loggers, sports accessories, and other devices) to import products that integrate semiconductor devices embodying inventions claimed in the '330 patent, or to sell or use such products, or offer them for sale, in the United States.

- 51. Defendants encourage customers, resellers, OEMs, or others to import into the United States and sell and use in the United States the '330 Accused Products embodying inventions claimed in the '330 patent with knowledge and the specific intent to cause the acts of direct infringement performed by these third parties. On information and belief, after Defendants obtained knowledge of the '330 patent, the '330 Accused Products have been and will continue to be imported into the United States and sold in large volumes by themselves and by others, such as customers, distributors, and resellers. Defendants are aware that the '330 Accused Products are integral components of the computer and mobile products incorporating them, that the infringing semiconductor devices are built into the computer and other products, and cannot be removed or disabled by a purchaser of the consumer products containing the

7

8 9

12

13

10

11

14 15

16

1718

19

20

21

22

2324

2425

26

27

United States. When OEMs, manu Complaint for Patent Infringement

Case No. 3:17-cv-07206

infringing semiconductor devices, such that Defendants' customers will infringe one or more claims of the '330 patent by incorporating such semiconductor devices in other products, and that subsequent importation, sale, and use of such products in the United States would be a direct infringement of the '330 patent. Therefore, Defendants are aware that their customers will infringe one or more claims of the '330 patent by selling, offering for sale, importing, and/or using the products as-sold and as-marketed by Defendants.

52. Defendants directly benefit from and actively and knowingly encourage customers', resellers', and users' importation of these products into the United States and sale and use within the United States. Defendants actively encourage customers and downstream users, OEMs, and resellers to import, use, and sell in the United States the '330 Accused Products that they manufacture and supply, including through advertising, marketing, and sales activities directed at United States sales. On information and belief, Defendants are aware of the size and importance of the United States market for customers of Defendants' products, and also distribute or supply these products intended for importation, use, and sale in the United States. Defendants routinely market their infringing semiconductor devices to third parties for inclusion in products that are sold to customers in the United States, as well as directly to end-user customers. For example, Defendants have publicly stated that their semiconductor devices are primarily targeted for use in industrial, automotive, and consumer electronics, including mobile phones, tablets, computers, cameras, set-top boxes, global positioning receivers, data loggers, sports accessories, networking devices, IoT devices, power conversion devices, and metering devices for smart grids. Further, Defendants have stated that their positioning receiver products are primarily targeted for handheld computers, cameras, data loggers, sports accessories, and other products, all of which are widely sold and used in the United States. Defendants have numerous direct sales, distributors, and reseller outlets for these products in the United States. Defendants' marketing efforts show that they have specifically intended to and have induced direct infringement in the United States.

53. Defendants also provide OEMs, manufacturers, importers, resellers, customers, and end users instructions, user guides, and technical specifications on how to incorporate the '330 Accused Products into electronics products that are made, used, sold, offered for sale in, and/or imported into the United States. When OEMs, manufacturers, importers, resellers, customers, and end users follow such

instructions, user guides, and technical specifications and embed the products in end products and make, use, offer to sell, sell, or import into the United States, they directly infringe one or more claims of the '330 patent. Defendants know that by providing such instructions, user guides, and technical specifications, OEMs, manufacturers, importers, resellers, customers, and end users follow them, and therefore directly infringe one or more claims of the '330 patent. Defendants thus know that their actions actively induce infringement.

54. Defendants have engaged and will continue to engage in additional activities to

- 54. Defendants have engaged and will continue to engage in additional activities to specifically target the United States market for the '330 Accused Products and actively induce OEMs, manufacturers, importers, resellers, customers, and end users to directly infringe one or more claims of the '330 patent in the United States. For example, Defendants have showcased their positioning receiver technologies at various industry events and through written materials distributed in the United States, in an effort to encourage various OEMs, manufacturers, importers, resellers, customers, and end users to include the infringing technology in their computers, mobile devices, data loggers, sports accessories, and other products. These events are attended by the direct infringers mentioned above and generally by companies that make, use, offer to sell, sell, or import in the United States products that use semiconductor devices such as those made by Defendants.

- 55. Defendants derive significant revenue by selling the '330 Accused Products to third parties who directly infringe the '330 patent in the United States. Defendants' extensive sales and marketing efforts, sales volume, and partnerships all evidence their intent to induce companies to infringe one or more claims of the '330 patent by, using, offering to sell, selling, or importing products that incorporate the '330 Accused Products, in the United States. Defendants have had specific intent to induce infringement or have been willfully blind to the direct infringement they are inducing.

- 56. Upon information and belief, Defendants have continued and will continue to engage in activities constituting contributory infringement of the '330 patent, including at least claims 1, 4, and 5, pursuant to 35 U.S.C. § 271(c). Defendants contributorily infringe with knowledge that the '330 Accused Products, or the use thereof, infringe the '330 patent. Defendants knowingly and intentionally contributed to the direct infringement of the '330 patent by others by supplying these semiconductor devices that embody a material part of the claimed invention of the '330 patent and that are known by Defendants to

be specially made or adapted for use in an infringing manner. For example, and without limitation, the 2 '330 Accused Products are used in end products, including computers, laptops, tablets, mobile telephones, 3 cameras, data loggers, and sports accessories. The '330 Accused Products are not staple articles or commodities of commerce suitable for non-infringing use and are especially made for or adapted for use in infringing the '330 patent. There are no substantial uses of the '330 Accused Products that do not 6 infringe the '330 patent. By contributing a material part of the infringing computing products sold, offered for sale, imported, and used by its customers, resellers, and users, Defendants have been and are now 8 indirectly infringing the '330 patent pursuant to 35 U.S.C. § 271(c).

- 57. Defendants' direct and indirect infringement of the '330 patent has injured Lone Star, and Lone Star is entitled to recover damages adequate to compensate for such infringement pursuant to 35 U.S.C. § 284. Unless it ceases its infringing activities, Defendants will continue to injure Lone Star by infringing the '330 patent.

- 58. On information and belief, Defendants acted egregiously and with willful misconduct in that their actions constituted direct or indirect infringement of a valid patent, and this was either known or so obvious that Defendants should have known about it. Defendants continue to infringe the '330 patent by using, selling, offering for sale, and importing in the United States the '330 Accused Products and to induce the direct infringement of others performing these acts, or they have acted at least in reckless disregard of Lone Star's patent rights. On information and belief, Defendants will continue their infringement notwithstanding actual knowledge of the '330 patent and without a good faith basis to believe that their activities do not infringe any valid claim of the '330 patent. All infringement of the '330 patent following Defendants' knowledge of the '330 patent is willful and Lone Star is entitled to treble damages and attorneys' fees and costs incurred in this action under 35 U.S.C. §§ 284 and 285.

#### PRAYER FOR RELIEF

#### WHEREFORE, Plaintiffs prays for:

- 1. Judgment that the '188, '933, and '330 patents are each valid and enforceable;

- 2. Judgment that the '188, '933, and '330 patents are infringed by Defendants;

- 3. Judgment that Defendants' acts of patent infringement relating to the patents are willful;

27

5

7

9

10

11

12

13

15

16

17

18

19

20

21

22

23

24

25

26

| 1  | 4. An award of damages arising out of Defendants' acts of patent infringement, together with              |  |  |  |  |

|----|-----------------------------------------------------------------------------------------------------------|--|--|--|--|

| 2  | pre-judgment and post-judgment interest;                                                                  |  |  |  |  |

| 3  | 5. Judgment that the damages so adjudged be trebled in accordance with 35 U.S.C. § 284;                   |  |  |  |  |

| 4  | 6. An award of Plaintiff's attorneys' fees, costs, and expenses incurred in this action in                |  |  |  |  |

| 5  | accordance with 35 U.S.C. § 285; and                                                                      |  |  |  |  |

| 6  | 7. Such other and further relief as the Court may deem just and proper.                                   |  |  |  |  |

| 7  | JURY DEMAND                                                                                               |  |  |  |  |

| 8  | Plaintiff demands trial by jury of all issues triable of right by a jury.                                 |  |  |  |  |

| 9  | RESERVATION OF RIGHTS                                                                                     |  |  |  |  |

| 10 | Plaintiff's investigation is ongoing, and certain material information remains in the sole possession     |  |  |  |  |

| 11 | of Defendants or third parties, which will be obtained via discovery herein. Plaintiff expressly reserves |  |  |  |  |

| 12 | the right to amend or supplement the causes of action set forth herein in accordance with Rule 15 of the  |  |  |  |  |

| 13 | Federal Rules of Civil Procedure.                                                                         |  |  |  |  |

| 14 | Respectfully submitted,                                                                                   |  |  |  |  |

| 15 |                                                                                                           |  |  |  |  |

| 16 | Dated: December 19, 2017  /s/ Jon A. Birmingham  Lon A. Birmingham  CA SBN 271024)                        |  |  |  |  |

| 17 | Jon A. Birmingham (CA SBN 271034)                                                                         |  |  |  |  |

| 18 | Attorney for Plaintiff LONE STAR SILICON INNOVATIONS LLC                                                  |  |  |  |  |

| 19 |                                                                                                           |  |  |  |  |

| 20 |                                                                                                           |  |  |  |  |

| 21 |                                                                                                           |  |  |  |  |

| 22 |                                                                                                           |  |  |  |  |

| 23 |                                                                                                           |  |  |  |  |

| 24 |                                                                                                           |  |  |  |  |

| 25 |                                                                                                           |  |  |  |  |

| 26 |                                                                                                           |  |  |  |  |

| 27 |                                                                                                           |  |  |  |  |

| 28 |                                                                                                           |  |  |  |  |

# **EXHIBIT** A

US005912188*A*

### United States Patent [19]

Gardner et al.

[11] Patent Number: 5,912,188

[45] **Date of Patent:** Jun. 15, 1999

#### [54] METHOD OF FORMING A CONTACT HOLE IN AN INTERLEVEL DIELECTRIC LAYER USING DUAL ETCH STOPS

[75] Inventors: Mark I. Gardner, Cedar Creek; Daniel Kadosh; Frederick N. Hause, both of

Austin, all of Tex.

[73] Assignee: Advanced Micro Devices, Inc.,

Sunnyvale, Calif.

[21] Appl. No.: 08/905,686

[22] Filed: Aug. 4, 1997

#### [56] References Cited

#### U.S. PATENT DOCUMENTS

| 4,943,539 7/19<br>5,110,712 5/19<br>5,162,260 11/19<br>5,275,972 1/19<br>5,451,543 9/19<br>5,472,825 12/19 | 88 Erie et al |  |

|------------------------------------------------------------------------------------------------------------|---------------|--|

|------------------------------------------------------------------------------------------------------------|---------------|--|

## OTHER PUBLICATIONS

Wolf, Stanley, Silicon Processing for the VLSI Era, vol. 2: Process Integration, Lattice Press, Sunset Beach, California, 1990, pp. 101–111; 189–199; 240–259; 276–283. Higelin, G. et al., "Double Level Interconnection System For Submicron CMOS Applications," VLSI Multilevel Interconnection Conference, Jun. 13–14, 1988, pp. 29–34.

Primary Examiner—William Powell Attorney, Agent, or Firm—Skjerven, Morrill, MacPherson, Franklin & Friel, L.L.P.

#### [57] ABSTRACT

A method of forming a contact hole in an interlevel dielectric layer using dual etch stops includes the steps of providing a semiconductor substrate, forming a gate over the substrate, forming a source/drain region in the substrate, providing a source/drain contact electrically coupled to the source/drain region, forming an interlevel dielectric layer that includes first, second and third dielectric layers over the source/drain contact, forming an etch mask over the interlevel dielectric layer, applying a first etch which is highly selective of the first dielectric layer with respect to the second dielectric layer through an opening in the etch mask using the second dielectric layer as an etch stop, thereby forming a first hole in the first dielectric layer that extends to the second dielectric layer without extending to the third dielectric layer, applying a second etch which is highly selective of the second dielectric layer with respect to the third dielectric layer through the opening in the etch mask using the third dielectric layer as an etch stop, thereby forming a second hole in the second dielectric layer that extends to the third dielectric layer without extending to the source/drain contact, and applying a third etch which is highly selective of the third dielectric layer with respect to the source/drain contact through the opening in the etch mask, thereby forming a third hole in the third dielectric layer that extends to the source/drain contact, wherein the first, second and third holes in combination provide the contact hole. In this manner, the contact hole is formed in the interlevel dielectric without any appreciable gouging of the underlying materials.

#### 30 Claims, 4 Drawing Sheets

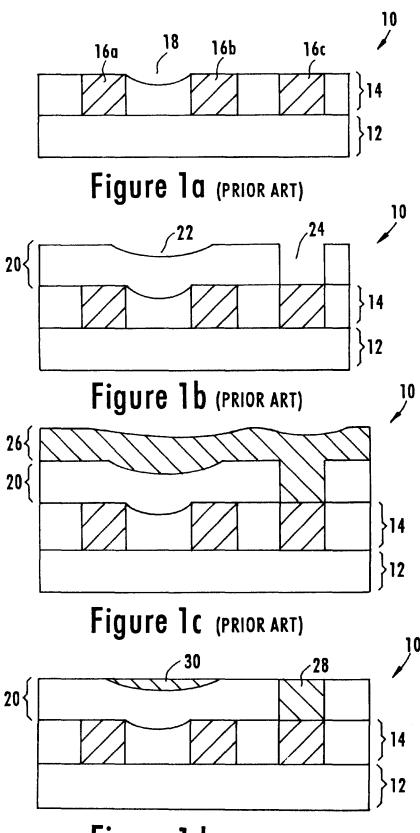

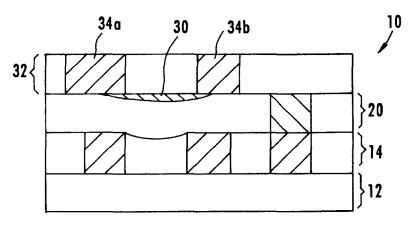

Jun. 15, 1999

Sheet 1 of 4

FIG. 1A

FIG. 1B

FIG. 1C

Jun. 15, 1999

Sheet 2 of 4

FIG. 1D

FIG. 1E

FIG. 1F

Jun. 15, 1999

Sheet 3 of 4

FIG. 1H

FIG. 1I

Jun. 15, 1999

Sheet 4 of 4

FIG. 1J

5,912,188

1

#### METHOD OF FORMING A CONTACT HOLE IN AN INTERLEVEL DIELECTRIC LAYER USING DUAL ETCH STOPS

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention relates to integrated circuit manufacturing, and more particularly to forming a contact hole in an interlevel dielectric layer.

#### 2. Description of Related Art

An insulated-gate field-effect transistor (IGFET), such as a metal-oxide semiconductor field-effect transistor (MOSFET), uses a gate to control an underlying surface channel joining a source and a drain. The channel, source and drain are located in a semiconductor substrate, with the source and drain being doped oppositely to the substrate. The gate is separated from the semiconductor substrate by a thin insulating layer such as a gate oxide. The operation of the IGFET involves application of an input voltage to the 20 gate, which sets up a transverse electric field in the channel in order to modulate the longitudinal conductance of the channel.

Refractory metal silicides are frequently used to provide low resistance contacts for the gate, source and drain. With this approach, a thin layer of refractory metal is deposited over the structure, and heat is applied to form a silicide wherever the refractory metal is adjacent to silicon (including single crystal silicon and polysilicon). Thereafter, an etch is applied that removes unreacted refractory metal to prevent bridging, silicide contacts for the gate, source and drain.

The devices must be selectively interconnected to form circuit patterns. As one approach, a first interlevel dielectric is formed over the substrate, first contact holes (or vias) are etched in the first interlevel dielectric to expose the silicide contacts, first metal plugs are formed in the first contact holes, and a metal-1 pattern is formed over the first interlevel dielectric that selectively interconnects the first metal plugs. Thereafter, a second interlevel dielectric is formed over the metal-1 pattern, second contact holes are etched in the second interlevel dielectric to expose the metal-1 pattern, second metal plugs are formed in the second contact holes, and a metal-2 pattern is formed over the second interlevel dielectric that selectively interconnects the second metal plugs. Additional interlevel dielectrics and metal patterns (such as metal-3, metal-4 and metal-5) can be formed in a similar manner.

Forming contact holes in the first interlevel dielectric is a key step in the fabrication of multilevel interconnect structures. The minimum size of the contact holes is usually determined by the minimum resolution of the optical lithography tool. When contact holes are larger than about 2.0 microns, wet etching is often used. However, the isotropic nature of wet chemical etching makes it generally unsuitable for patterning submicron contact holes. Since the first interlevel dielectric is typically silicon dioxide, dry etching for silicon dioxide is often used to form submicron contact holes.

Dry etching silicon dioxide typically involves a plasma etching procedure in which a plasma generates reactive gas species that chemically etch the material in direct proximity to the plasma. The ability to achieve anisotropic etching requires bombardment of the silicon dioxide with energetic 65 ions. Other parameters such as the chemical nature of the plasma also influence the degree of anisotropy. In general,

2

the etch is highly anisotropic and forms contact holes with straight vertical sidewalls that taper slightly. The etch rate depends on several factors including pressure, power, feed gas composition, and film characteristics. For instance, thermally grown silicon dioxide etches more slowly than chemical vapor deposited silicon dioxide. In addition, the etch can be highly selective of silicon dioxide with respect to underlying silicon.

Dry etch equipment requires the availability of effective end-point detection tools for reducing the degree of overetching, increasing throughput and achieving run-to-run reproducibility. Four common methods for determining the end-point of dry etch processes are 1) laser interferometry and reflectivity, 2) optical emission spectroscopy, 3) direct observation through a viewing port on the chamber by a human operator, and 4) mass spectroscopy. End-point detection of contact holes can be difficult because the total area being etched is quite small compared to other layers.

Furthermore, in many integrated circuits, individual devices in various areas are arranged in different configurations and densities. For example, some integrated circuits include devices having a wide range of functionality with the variability of functionality being reflected in a variability of layout configuration. One implication arising from the variability of configuration is that some areas of the integrated circuit are densely populated with devices while other areas include only relatively isolated devices.

Applicant has observed that when silicon dioxide is dry etched, the etch rate of contact holes is often slower in densely populated areas of the substrate (with a high density of contact holes) than in sparsely populated areas of the substrate (with a low density of contact holes). The difference in etch rates may result from poorly-understood aspects of the chemistry of the plasma etching, such as increasing the rate of reactive ion etching in areas having a low density of contact holes and therefore less of the silicon dioxide layer exposed to the etch. Irrespective of the causes, since etched silicon beneath certain contact holes may be detected before other contact holes are completely etched, an overetch becomes necessary to ensure complete formation of all the contact holes. Unfortunately, the overetching can cause appreciable gouging of the underlying materials beneath the contact holes. For instance, the overetching can damage the silicon surface of source/drain regions, damage or remove thin silicide contacts, remove substantial portions of oxide spacers adjacent to the gate, and/or remove substantial portions of field oxides such as trench oxides or LOCOS in the substrate. The gouging increases the potential for excessive leakage current as well as device failure.

One solution known in the art is to form an interlevel dielectric layer with a thick silicon dioxide layer on a thin silicon nitride layer. A first etch is applied which is highly selective of silicon dioxide with respect to silicon nitride to form holes in the silicon dioxide layer using the silicon nitride layer as an etch stop. This allows the first etch to have a sufficiently long duration without damaging the underlying materials. Thereafter, a second etch is briefly applied which is highly selective of silicon nitride to complete formation of the contact hole. A drawback to this approach, however, is that the second etch is usually highly selective of silicon as well. As a result, substantial damage to an underlying silicon surface may arise.

Accordingly, a need exists for a method of forming a contact hole in an interlevel dielectric without appreciably gouging the underlying materials.

5,912,188

3

#### SUMMARY OF THE INVENTION

An object of the invention is to provide a contact hole in an interlevel dielectric without any appreciable gouging of the underlying materials. Generally speaking, this is accomplished by forming an interlevel dielectric with first, second and third dielectric layers, etching a first hole in the first dielectric layer using the second dielectric layer as an etch stop, etching a second hole in the second dielectric layer using the third dielectric layer as an etch stop, and etching a third hole in the third dielectric layer.

In accordance with one aspect of the invention, a method of forming a contact hole in an interlevel dielectric laver using dual etch stops includes the steps of providing a semiconductor substrate, forming a gate over the substrate, forming a source/drain region in the substrate, providing a source/drain contact electrically coupled to the source/drain region, forming an interlevel dielectric layer that includes first, second and third dielectric layers over the source/drain contact, forming an etch mask over the interlevel dielectric layer, applying a first etch which is highly selective of the first dielectric layer with respect to the second dielectric layer through an opening in the etch mask using the second dielectric layer as an etch stop, thereby forming a first hole in the first dielectric layer that extends to the second dielectric layer without extending to the third dielectric layer, applying a second etch which is highly selective of the second dielectric layer with respect to the third dielectric layer through the opening in the etch mask using the third dielectric layer as an etch stop, thereby forming a second hole in the second dielectric layer that extends to the third dielectric layer without extending to the source/drain contact, and applying a third etch which is highly selective of the third dielectric layer with respect to the source/drain contact through the opening in the etch mask, thereby forming a third hole in the third dielectric layer that extends to the source/drain contact, wherein the first, second and third holes in combination provide the contact hole.

Preferably, the first, second and third etches are anisotropic etches that form the contact hole with straight sidewalls, mechanical polishing before forming the etch mask. It is also preferred that the gate have a greater thickness than a combined thickness of the second and third dielectric layers, and that the first dielectric layer have a greater thickness than the gate.

As exemplary materials, the gate is polysilicon, the etch mask is photoresist, the first and third dielectric layers are silicon dioxide or silicon oxyfluoride, and the second dielectric layer is silicon nitride, silicon oxynitride, hydrogen phenylquinoxaline, polyquinoline, or methysilsesquixane

Advantageously, the first etch can have a long duration to ensure that the first hole is completely etched through a thick first dielectric layer without etching the third dielectric layer, 55 the second etch can be highly selective of the source/drain contact without etching the source/drain contact, and the third etch can have a brief duration and can be unselective of the source/drain contact to ensure that the third hole is completely etched through a thin third dielectric layer without any appreciable gouging to the source/drain contact. Moreover, even if the third etch is highly selective of other materials (such as oxide spacers or field oxide) beneath the contact hole, the brief duration of the third etch prevents any appreciable gouging to these materials as well.

Thereafter, a conductive plug can be formed in the contact hole, and a metal-1 pattern can be formed on the first

dielectric layer that contacts the conductive plug. If desired, the conductive plug can provide a local interconnect to a second source/drain contact exposed by the contact hole.

The source/drain contact can be a silicide contact formed on the source/drain region, or alternatively the source/drain contact can be the source/drain region itself.

These and other objects, features and advantages of the invention will be further described and more readily apparent from a review of the detailed description of the preferred embodiments which follows.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The following detailed description of the preferred 15 embodiments can best be understood when read in conjunction with the following drawings, in which:

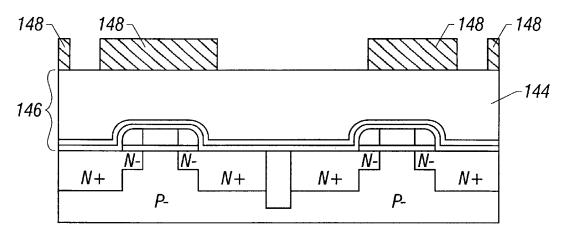

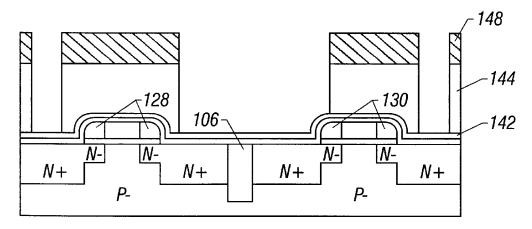

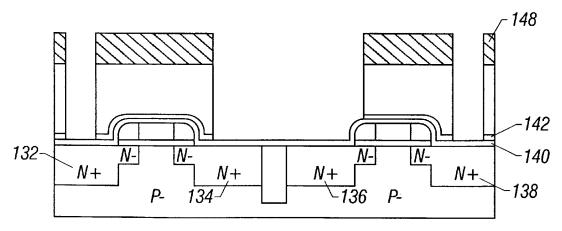

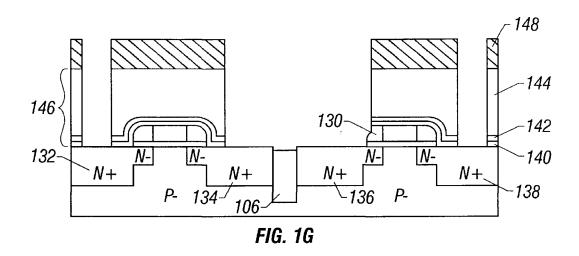

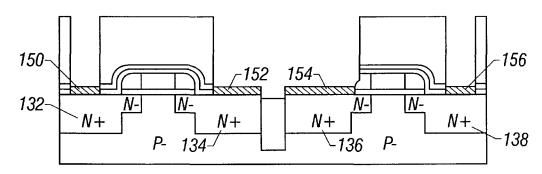

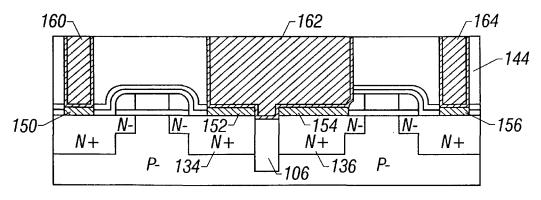

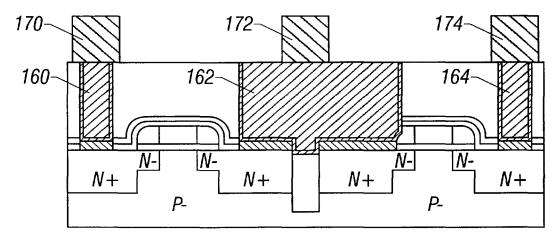

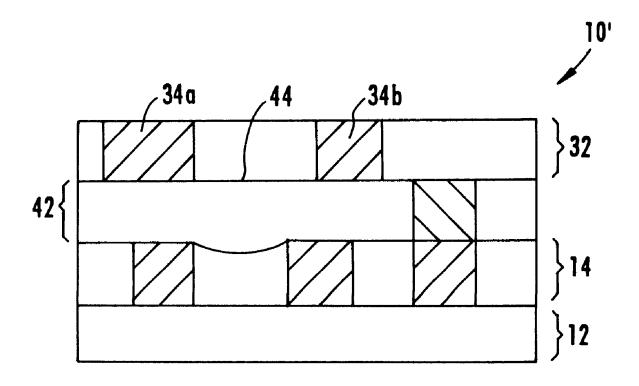

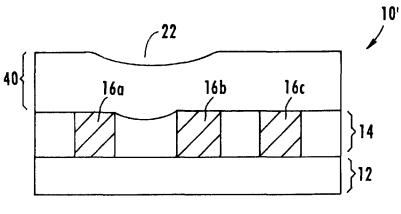

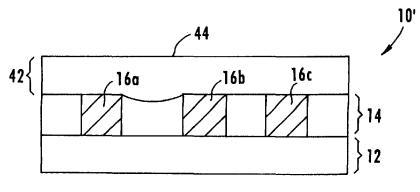

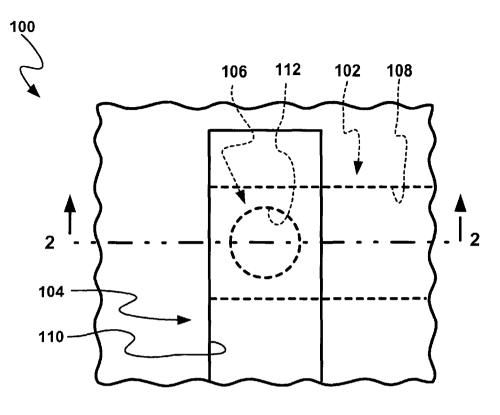

FIGS. 1A-1J show cross-sectional views of successive process steps for forming a contact hole in an interlevel dielectric layer in accordance with an embodiment of the 20 invention.

#### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

In the drawings, depicted elements are not necessarily drawn to scale and like or similar elements may be designated by the same reference numeral throughout the several

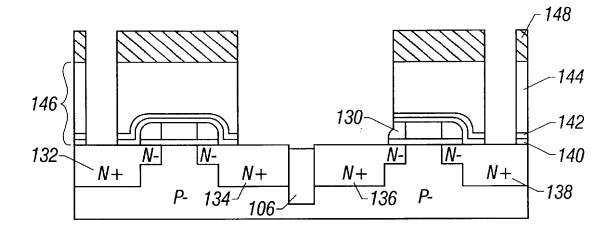

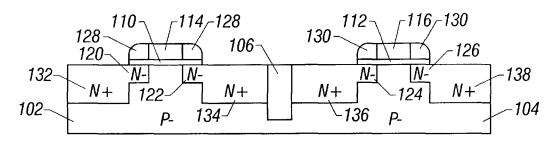

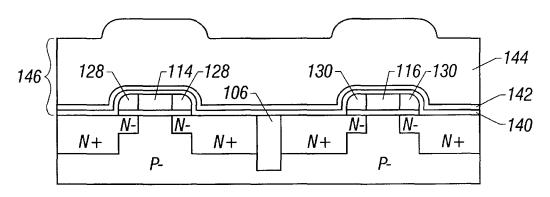

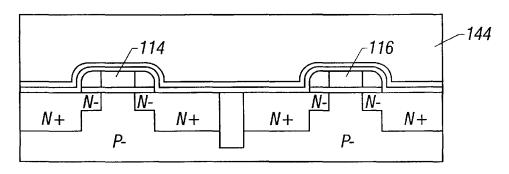

In FIG. 1A, a silicon substrate suitable for integrated 30 circuit manufacture is provided. The substrate includes a Ptype epitaxial surface layer on a P+ base layer (not shown). The epitaxial surface layer has a boron background concentration on the order of 1×10<sup>15</sup> atoms/cm<sup>3</sup>, a <100> orientation and a resistivity of 12 ohm-cm. Active regions 102 and 35 104 of the substrate are shown. Trench oxide 106 composed of silicon dioxide (SiO<sub>2</sub>) is formed in the substrate and provides dielectric isolation between active regions 102 and 104. Active regions 102 and 104 are subjected to a well implant, a punchthrough implant, and a threshold adjust and the interlevel dielectric layer is planarized by chemical- 40 implant. The well implant provides a more uniform background doping, the punchthrough implant provides greater robustness to punchthrough voltages, and the threshold voltage implant shifts the threshold voltage to a desired value such as 0.4 to 0.7 volts. Gate oxides 110 and 112 45 composed of silicon dioxide are formed on the top surface of active regions 102 and 104, respectively, using tube growth at a temperature of 700 to 1000° C. in an O<sub>2</sub> containing ambient. Thereafter, a polysilicon layer with a thickness of 2000 angstroms is deposited over the structure silsesquioxane, fluorinated polyimide, poly- 50 by chemical vapor deposition and patterned using photolithography and an etch step to form polysilicon gates 114 and 116 on gate oxides 110 and 112, respectively. Polysilicon gates 114 and 116 each have a length of 3500 angstroms between opposing sidewalls.

> Lightly doped source and drain regions 120 and 122 are implanted into active region 102 and lightly doped source and drain regions 124 and 126 are implanted into active region 104 by subjecting the structure to ion implantation of phosphorus, at a dose of  $1\times10^{13}$  to  $5\times10^{14}$  atoms/cm<sup>2</sup> and an energy of 2 to 35 kiloelectron-volts, using polysilicon gate 114 as an implant mask for active region 102 and using polysilicon gate 116 as an implant mask for active region 104. Lightly doped source and drain regions 120, 122, 124 and 126 are doped N- with a phosphorus concentration of  $1\times10^{17}$  to  $1\times10^{18}$  atoms/cm<sup>3</sup> and form channel junctions substantially aligned with the opposing sidewalls of polysilicon gates 114 and 116. Thereafter, an oxide layer with a